智算网络路径质量三要素:带宽/队列/时延在智能选路中的协同优化

在长期服务于用户AI训练/推理生产网络的实践中,我们深刻观察到传统静态或简单度量(如跳数)的选路策略难以满足高性能AI集群网络的严苛要求。AI工作负载,特别是涉及大规模参数同步(如All-Reduce操作)和RDMA(如RoCEv2)流量时,对网络的带宽可用性、低延迟和极低抖动有着近乎极致的需求。

网络路径上的微小波动,如短暂拥塞导致的队列积压或转发延迟增加,都可能显著拖慢整个训练作业的完成时间,造成昂贵的算力资源浪费。

智能选路的路径质量如何判定?

为了从根本上优化AI流量的传输效率并最大化集群利用率,我们设计并实践了基于多维度网络状态感知的动态智能选路技术。该技术的核心创新在于,聚焦关键影响因子,摒弃单一指标,精准识别并引入在AI集群网络环境中对性能影响最为显著的动态参数作为核心计算因子:

- 实时带宽利用率:精确测量路径上关键链路的当前可用带宽。避免将高吞吐量的AI流量(如梯度同步)引导至已接近饱和的链路,防止拥塞崩溃和PFC反压风暴。

- 队列深度/使用情况: 直接监控网络设备(交换机)出口队列的瞬时和平均深度。队列深度是拥塞的先行指标,深度过大意味着数据包排队等待时间(Bufferbloat)增加,直接导致传输延迟上升和抖动加剧,这对依赖确定性的RDMA和集合通信操作是致命的。

- 转发时延/延迟变化: 不仅测量路径的基础传播延迟,更关键的是持续监测数据包转发处理延迟及其变化(抖动)。这反映了设备本身的处理能力和当前负载状态,高或波动的处理时延会破坏AI流量的同步性。

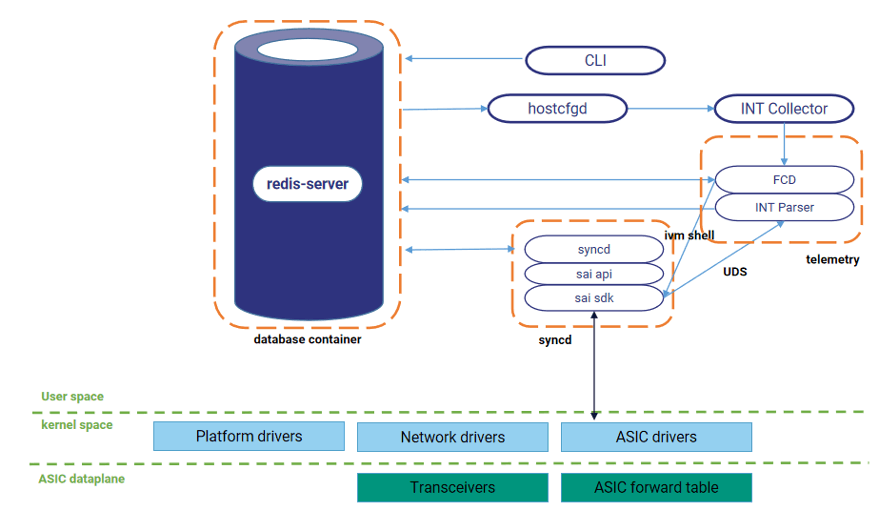

智能选路中的统计计数:ASIC赋能的高精度数据采集

在动态智能选路系统的实现中,带宽利用率与队列深度这两大关键指标的采集直接依赖于网络设备的ASIC硬件级能力。具体而言:

硬件级实时监测(百毫秒级精度)

ASIC芯片内置的硬件寄存器持续执行线速统计,对每个端口的字节转发计数(Byte Counter) 和各优先级队列的缓存占用计数(Queue Depth Counter) 进行原子级累加。这种基于硅片级电路的计数机制摆脱了软件轮询的延迟与性能开销,可实现百毫秒级精度的数据捕获,精准反映瞬时网络拥塞状态。

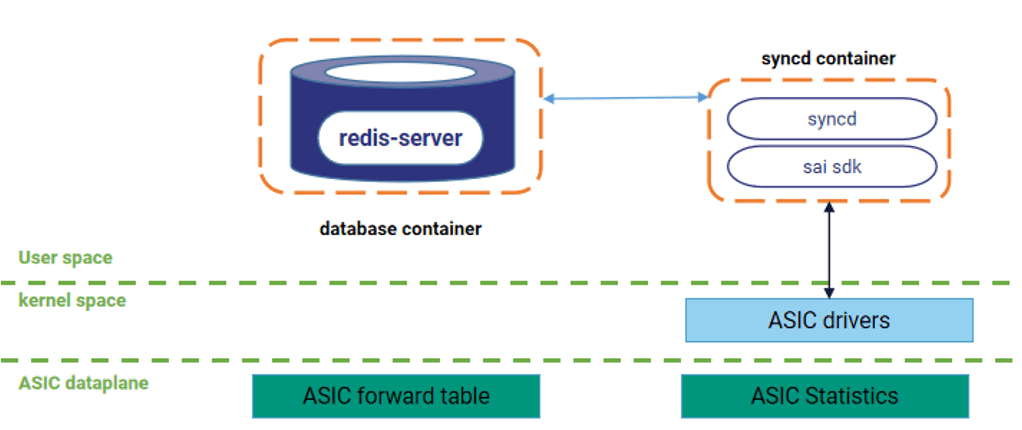

控制面高效采集(亚秒级同步)

运行于设备控制面的SONiC网络操作系统,通过标准化的SAI(Switch Abstraction Interface)接口以亚秒级周期(通常为500ms) 主动读取ASIC寄存器的统计快照。此设计确保控制面能够近乎实时地感知转发芯片的状态变化,为动态选路提供高时效性数据输入。

流水线式数据处理与存储

采集的原始计数器数据通过以下高效流水线处理:

- ① 增量计算:SAI层将本次读数与上次读数做差,计算出时间窗口内的实际流量增量(ΔBytes)与队列深度变化值(ΔQueue-Occupancy)。

- ② Redis高速缓存:处理后的增量数据被写入内存数据库Redis的时序结构(TSDB)中,形成带时间戳的指标序列。此架构满足高吞吐、低延迟的数据存取需求,为后续分析提供支撑。

BGP宣告的优化设计(秒级间隔)

若按ASIC的亚秒级精度(如每100ms)通过BGP宣告路径质量,会导致控制面压力剧增,频繁生成和传输BGP Update消息,占用CPU和带宽资源。微秒级变化也可能触发不必要的路由更新,影响网络稳定性。所以,采用秒级间隔(例如每秒1次)向邻居发送BGP Update消息,携带加权平均后的路径质量值。路径质量通过BGP扩展社区属性(如Path Bandwidth Extended Community)传递,格式为浮点数(单位Gb/s)

纳秒级时延测量:INT与HDC技术负载均衡中的深度应用

转发时延计算因子基于INT(In-band Network Telemetry)技术,精度可达纳秒级。HDC(High Delay Capture)是一种能捕获ASIC中经历高延迟的数据包信息的INT技术。

INT硬件流水线实现原理

数据包进入交换机ASIC时,入口流水线在包头插入INT Shim头部,并记录精确入端口时间戳(基于芯片级高精度时钟,分辨率达纳秒级)。转发过程中,每个流水线阶段(如Ingress/Egress队列)实时追加时延元数据。包离开出口队列时,ASIC计算,此设计消除了交换机基础转发延迟的影响,仅保留队列排队时延这一关键变量。

HDC(高延迟捕获)技术深度解析

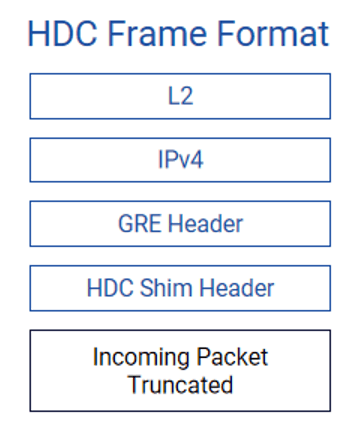

HDC是INT的功能扩展,专为捕捉网络中的尾延迟(Tail Latency) 事件设计。只捕获超过用户预设阈值(如10μs)的异常延迟报文,实现靶向抓包而非全量监控。ASIC硬件实时比对报文时延与阈值——当报文在队列/缓存中的滞留时间超过阈值,立即触发抓取动作。并将原始数据包的前150字节连同INT元数据(包含出入端口、时延等关键信息)作为HDC数据包发送到收集器。

动态阈值触发机制

- 用户可基于业务需求设置多级延迟阈值(如:关键RDMA流:>5μs、普通TCP流:>50μs)

- ASIC硬件实时比对每个包的实际队列时延与阈值,触发零拷贝抓包。

元数据结构化封装

HDC告警包包含两类关键信息:

- 原始包摘要:截取L2-L4层头部(150字节),保留五元组、TCP标志位等特征

- INT元数据:

落地实践:AI RoCE交换机上的智能选路

动态智能选路技术在星融元交换机上开启HDC功能,并将CPU作为HDC的收集分析器,通过分析HDC报文实现高精度测量交换机转发时延,并将时延信息作为路径质量评价因子,提高路径质量评价精度。