Read more

Why People Choose to Deploy Open Source DPU Smart NICs in Their Data Centers

As we known,the growth of data center server

arithmetic power can no longer keep up with the growth of bandwidth, and the arithmetic power originally used to process business is heavily wasted on processing network data and infrastructure business (OVS, NFV), and the performance by way of CPU software emulation can no longer meet the demand, and server performance has reached a bottleneck, and many customers in the market may consider two options:

- Increase the number of servers;

- Adding a SmartNIC to the server for network service offload. Obviously, the cost consumed to increase the number of servers is much larger than to purchase smartNICs.

Open Source DPU SmartNIC for CPU Offload

On traditional smart NICs, the processing of the first packet is on the CPU, and the flow table is sent down to the NIC chip still occupies CPU resources, and the interface and related protocols need to be defined for the offloaded service, which is complicated to implement and difficult to locate the problem.

On the other hand, on the SmartNIC of DPU architecture, full offload can be realized without much business interface between each other, and the positioning problem is clear. It is equivalent to having dedicated computing resources to deal with the control plane associated with the smart NIC, which can realize the full offload of the control plane + forwarding plane, and the processing performance of DPU is at an absolute advantage compared with the NIC of FPGA or SoC architecture.

Take cloud gateway access as an example. Under the premise of ensuring the total number of access users, the construction solution of introducing DPU architecture intelligent NIC has obvious advantages in rack space occupation, total power consumption and cost compared with the construction solution of pure 2U server. Among them, the rack space saving is more than 2/3, the total power consumption saving is more than 1/2, the construction cost saving is 8W, while the average number of users per U access on the rack is more than 3 times.

Application Scenarios for Helium DPU SmartNICs

Asterfusion Helium SmartNIC based on Marvell OCTEON TX CN9670 which contains 24 -core ARM processors with 2 ×100G QSFP28 ports/ 4×25G SFP28 ports,along with multiple integrated hardware-acceleration co-processors that accelerates workloads for data center, cloud, Web2.0, security and storage scenarios.

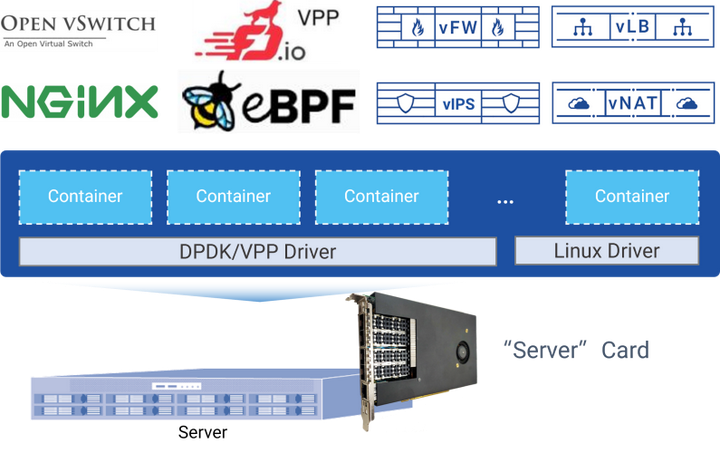

Example 1: Open vSwitch (OVS) offload to Helium DPU SmartNIC with third-party application integration

-图1-1024x483.jpg)

- Enables installation of various container application features on the card

- Open up data channels between containers and between containers and VMs

Example 2: Helium DPU Smart NIC offloads SSL encryption engine

-图2-1024x492.jpg)

- Built-in hardware encryption and decryption engine

- SSL encryption and decryption: 29K TPS; 10~20Gbps

Example 3: Helium DPU Smart NIC offloads eBPF

-图3-1024x803.jpg)

The eBPF function is offloaded to the smart NIC. The ARM processor carried on the smart NIC implements a separate backend, compiles the intermediate eBPF bytecode into the instruction code of the ARM processor architecture, loads it into the NIC RAM (the smart NIC contains DRAM, so MAP can also be offloaded), and the smart NIC loads the eBPF program from the NIC RAM and runs it

The eBPF processes the data packets and returns the metadata and statistics to the host application.

Example 4: Helium DPU Smart NIC completely offloads 5G UPF

-图4-1024x391.jpg)

- All UPF functions (signaling side and user side) are offloaded to the Smart NIC for seamless integration with the MEC Host

- UPF and MEC are logically isolated and do not affect each other, so MEC can obtain high performance without re-architecting

For more information, visit: https://asterfusion.com/product/helium_dpu/ or send email to sales@asterfusion.com