Read more

Introduction of an 100G open source DPU SmartNIC – Asterfusion Helium

From NICs to “SmartNICs”

The development of CPU computing power can not keep up with the demand for computing power, so it is considered that some of the original CPU-bearing functions can be offloaded to other dedicated hardware (such as network cards), thus releasing CPU computing power and allowing it to focus on the critical (and economically beneficial) user business.

But this puts higher demands on the hardware used to offload the CPU . Not only do we need to send and receive traffic and other forwarding functions, but we also need the NIC to take on more diverse functions, transforming the traditional NIC into a “smart NIC”.

SmartNIC deployment in Data Centers

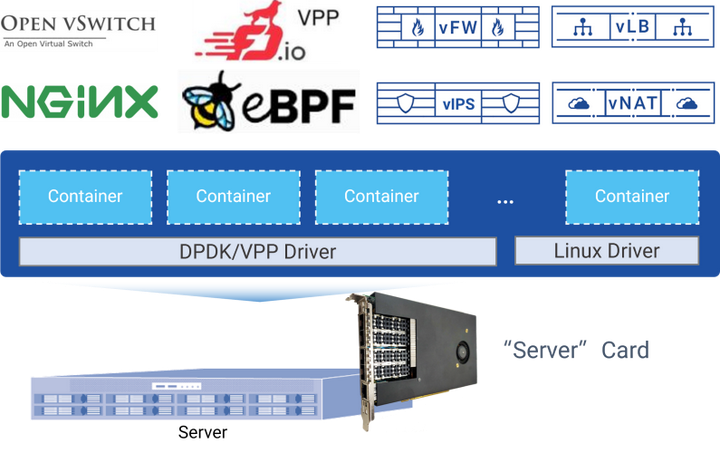

- Network acceleration: e.g. OVS offload/VXLAN termination, TCP offload, tunnel encapsulation/decapsulation such as GRE/GTP, reliable UDP, 5G UPF acceleration, etc.;

- Security acceleration: e.g. IPSec, SSL, XDP/eBPF, vFW/vLB/vNAT, DPI, DDoS, compression/decompression, etc;

- Storage acceleration: e.g. RDMA offload, NVMe-oF, etc.

What is a DPU architecture SmartNIC?

On traditional SmartNICs, the processing of the first packet is on the CPU, and the flow table down to the NIC chip still takes up CPU resources, and it needs to define interfaces and related protocols for the offloaded services, which is more complicated to implement and difficult to locate the problem. On the other hand, on the SmartNIC of DPU architecture, full offload can be realized without much business interface between each other and the positioning problem is clear. It is equivalent to having dedicated computing resources to deal with the control plane associated with the SmartNIC, which can realize the full offload of control plane + forwarding plane.

Comparing different types of SmartNICs

| ASIC | FPGA | SoC(Multi-core + ASIC) |

|---|---|---|

| —— | Low latency Low power consumption | High flexibility Offload control plane and forwarding plane |

| Poor programmability | Programmable, but high development difficulty Limited development of open source ecosystem Higher price | Higher power consumption |

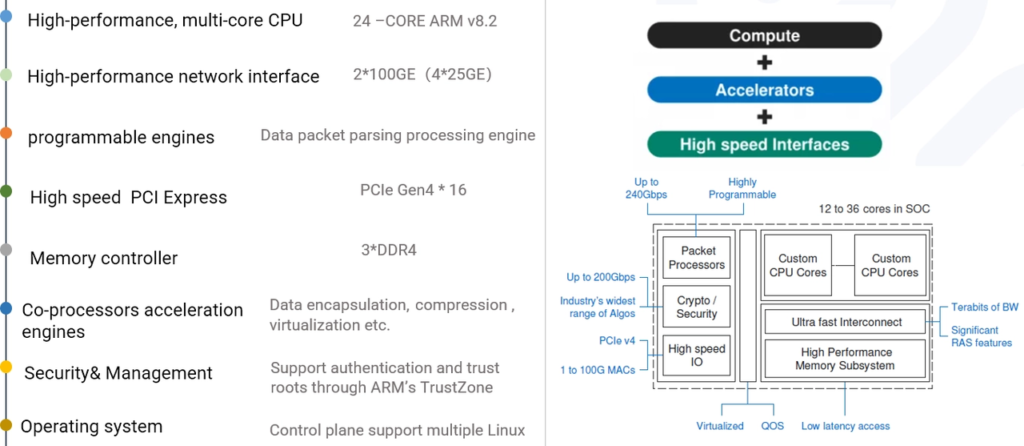

DPU architecture is a multi-core processor + ASIC on a single chip (SoC is to integrate them on the board, although DPU is more integrated but essentially similar architecture)

- CPU-based, easy to program and migrate from x86 servers

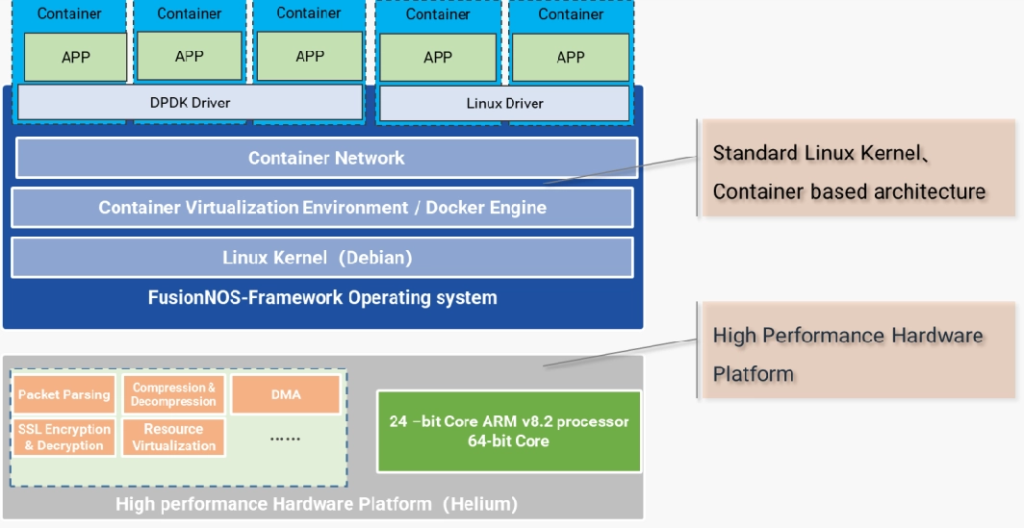

- Containerized deployment environment, different functions need to be offloaded in different containers, just like a small server, can achieve multiple functions at the same time

Introducing an open source DPU SmartNIC hardware—— Helium

Currently, Asterfusion has open-sourced the product information and code of Helium DPU SmartNIC, and invites all partners to build the industry ecology together!

Visit https://github.com/asterfusion/Helium_DPU

Helium DPU SmartNIC provides a fully open software development environment that can offload and accelerate the virtual network and virtual network functions that customers originally run on x86 servers in cloud data centers, HPC, edge computing and other scenarios, providing customers with a higher performance experience while reducing TCO.

Asterfusion Helium SmartNIC based on Marvell OCTEON TX CN9670 which contains 24 -core ARM processors with 2 ×100G QSFP28 ports/ 4×25G SFP28 ports,along with multiple integrated hardware-acceleration co-processors that accelerates workloads for data center, cloud, Web2.0, security and storage scenarios.

Asterfusion SmartNIC comes with a basic network operating system – FusionNOS, which can be used as the foundation to develop user’s upper-layer applications.

- Through a very simple compilation process various x86-based DPDK applications and generic Linux drivers can be easily ported to Asterfusion Helium SmartNIC.

- DPDK, VPP, SPDK and Ubuntu Support

参考资料: